| • 1.2GHz XBurst2 dual core CPU |

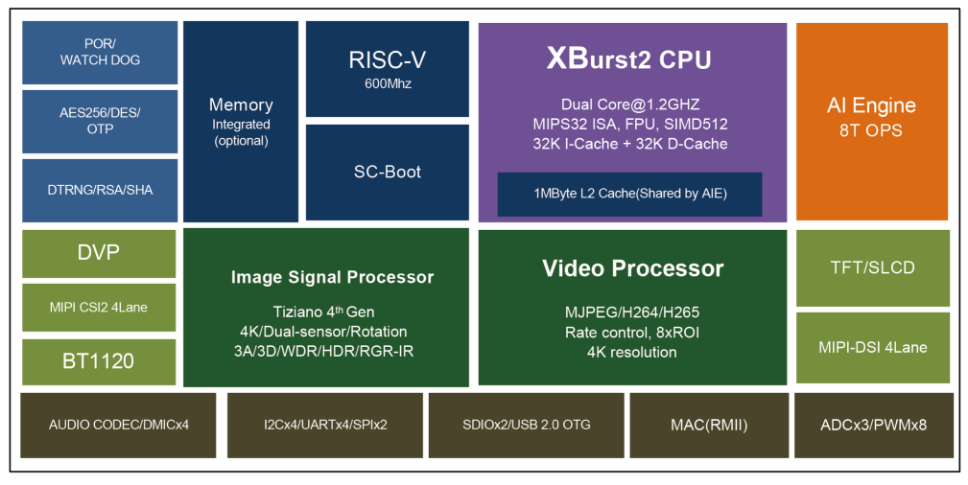

Block Diagram

Specifications

CPU | XBurst2 1.2GHz dual core maximum 1024KB Configurable L2 Cache SIMD512 instruction set |

MCU | 600MHz RISC-V coprocessor |

Memory | Maximum 2GB size Support DDR2/DDR3/DDR3L |

AIE | Built-in neural network accelerator Typical 8T OPS,support int16/int8/int4/int2 convolution width Built-in 1MB memory pool Built-in algorithm post/preprocessing acceleration unit Magik AI algorithm develop platform available |

Camera Interface | Support DVP/MIPI-CSI/BT1120/BT656 Sensor input interfaces Support stereo vision, dual sensor input, maximum 3 channels input |

ISP | Latest Tizano-III ISP engine Maximum 3840x2160 input and processing resolution Dual sensor processing, max 4M*2 Three channels output CH0@4K CH1@5M CH2@2M Support 3A/3D/WDR/HDR/rgb-ir Support LDC Support 90, 270 rotation |

Encoder | Support H.265/H.264/JPEG video encoding Maximum performance 3840x2160@25fps Built-in VBR/CBR/Fix QP all kind of bit rate control methods |

Display | Support TFT/SLCD display interfaces Support MIPI-DSI-4Lane display interfaces Maximum 1080P resolution display panel |

Audio | Built-in Audio Codec stereo AMIC input and mono output |

Boot | Support boot up from SPI Nor/SPI Nand/SD/USB Built-in Secure Boot logic, RSA2048+SHA256 protection algorithm Reset from RC or POR |

Peripherals

| ETH MAC SADC:4 Channels PWM x 8 SPI:Master x 2/Slave x 1 I2C x 4 UART x4 SDIO x 2 USB:2.0 OTG |

Smart Video